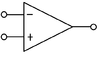

연산 증폭기 (Operational amplifier)는 한개의 차동 입력과 한개의 출력을 가지는 고이득 전압 증폭기다.

구조[편집 | 원본 편집]

이상적인 연산증폭기는 1개의 차동입력과 1개의 출력을 가지고 있으며, 실제 증폭기는 2개의 직류 입력(회로에서 +전압 VCC와 -전압 VEE로 표시된다)을 추가로 필요로 한다.

특성[편집 | 원본 편집]

이상적인 증폭기[편집 | 원본 편집]

이상적인(ideal) 연산 증폭기는 증폭비, 대역폭, 입력저항이 무한대이며, 출력저항이 0이다.

실제 증폭기[편집 | 원본 편집]

다만 실제 증폭기는 유한한 증폭비 (<106), 유한한 대역폭, 유한한 입력저항 등을 가진다. 회로 설계에 있어서 증폭기의 현실적인 특성을 무시하고 설계했다가는 설계자가 원하는 결과가 나오지 않을 수도 있다.

응용회로[편집 | 원본 편집]

신호 증폭, 발진회로, 계측, 연산, 잡음제거 등등 여러 분야에 사용된다.