하드웨어 기술 언어 (Hardware Description Language, HDL)는 논리회로의 구조와 동작을 기술하는 언어다. 시뮬레이션을 통해, 제작한 회로를 검증 할 수도 있다.

HDL의 필요성[편집 | 원본 편집]

|

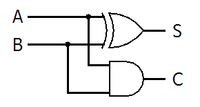

module half_adder(A, B, S, C); input A, B; output S, C; xor(S, A, B); and(C, A, B); endmodule |

| 반가산기의 논리 회로도 | 왼쪽의 회로도를 Verilog를 이용해 작성한 예시 |

겉보기에는 왼쪽이 오른쪽보다 쉬워보이므로,

“ 뭐 이런거 하는데 프로그래밍 언어 비슷한걸 배워서 해야하냐? 위에 반가산기 저거, 손으로 회로도 그리고 빵판에 게이트 붙이고 선 연걸해서 확인해보는게 빠르겠다! “

라고 따질 수 있지만, 안타깝게도(?) 기술 발달이 그걸 불가능하게 만들었다. 기술 발달로 칩 하나에 트랜지스터[1]가 수만~수십만개 이상이 들어갈 수 있게 설계를 해야하는데, 이 회로도를 손으로 그리는 것은 무리고, 그걸 알아보는 것도 무리, 이걸 빵판에 문제없이 구현하고 확인 및 수정하는 것도 무리다. 인텔 코어 i7-5960x 같은 경우, 칩에 트랜지스터가 약 19억개 정도 들어가 있다. 출처 당연히 설계 및 검증은 수작업으로는 불가능.

그러나 HDL을 사용하면 (언어를 배웠다는 가정하에) 상대적으로 알아보기 쉽고, 실물로 구현해서 확인하기 이전에 컴퓨터 시뮬레이션을 이용해서 어디에 문제가 있는지 파악 할 수 있다.

종류[편집 | 원본 편집]

각주

- ↑ 논리 게이트 하나에 트랜지스터가 여러 개 들어간다.