가산기(加算器, Adder)는 디지털 논리회로, 그 중에서도 조합논리회로(Combinational logic circuit)의 하나이다. 덧셈 연산을 수행한다.

종류[편집 | 원본 편집]

반가산기[편집 | 원본 편집]

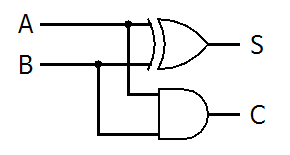

반가산기(Half adder)는 두 개의 입력을 받아서 그 합(sum)과 자리올림수(carry-out) 를 출력한다.

| 입력 | 출력 | ||

|---|---|---|---|

| A | B | Sum | Carry-out |

| 0 | 0 | 0 | 0 |

| 0 | 1 | 1 | 0 |

| 1 | 0 | 1 | 0 |

| 1 | 1 | 0 | 1 |

전가산기[편집 | 원본 편집]

전가산기(Full adder)는 두 개의 입력과 자리올림수 입력(Carry-in)을 받아 그 합과 자리올림수를 출력(Carry-out)한다. 반가산기는 하위 자리올림수를 받지 않으나, 전가산기는 자리올림수를 받아서 덧셈 연산을 한다. 전가산기를 여러 개 연결하면 임의의 자릿수에 대한 이진수 덧셈이 가능하다.

| 입력 | 출력 | |||

|---|---|---|---|---|

| A | B | Cin | Sum | Cout |

| 0 | 0 | 0 | 0 | 0 |

| 0 | 0 | 1 | 1 | 0 |

| 0 | 1 | 0 | 1 | 0 |

| 0 | 1 | 1 | 0 | 1 |

| 1 | 0 | 0 | 1 | 0 |

| 1 | 0 | 1 | 0 | 1 |

| 1 | 1 | 0 | 0 | 1 |

| 1 | 1 | 1 | 1 | 1 |

리플 캐리 가산기[편집 | 원본 편집]

이 문단은 비어 있습니다. 내용을 추가해 주세요.

자리올림수 예측 가산기[편집 | 원본 편집]

이 문단은 비어 있습니다. 내용을 추가해 주세요.

자리올림수 저장 가산기[편집 | 원본 편집]

이 문단은 비어 있습니다. 내용을 추가해 주세요.